UCIe Is the Boring Standard That Changes Everything

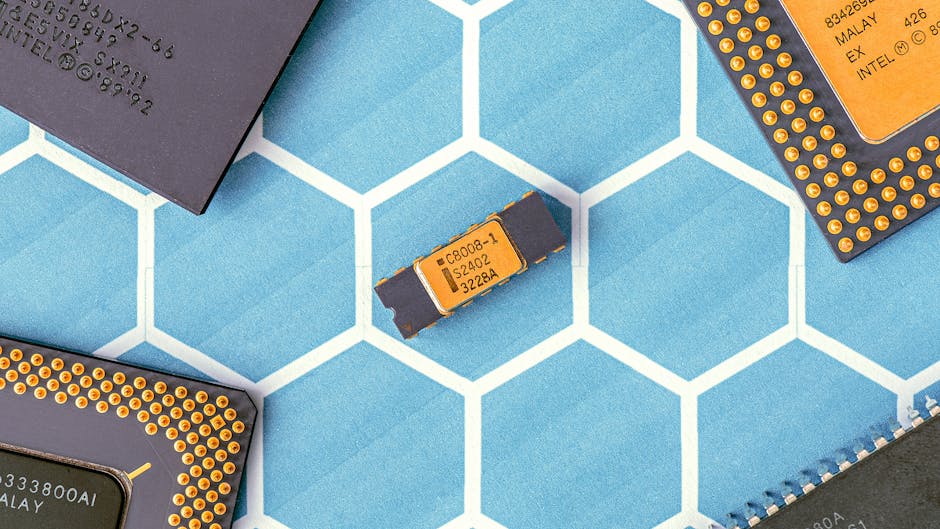

Standards are never exciting until they win. USB was boring. PCIe was boring. Ethernet was boring. Each one unlocked an ecosystem worth trillions. UCIe -- the Universal Chiplet Interconnect Express -- is the next boring standard that matters.

The problem UCIe solves is fundamental. Chiplets are the future of semiconductor design. That much is consensus. But chiplets from different vendors, different process nodes, and different foundries need to talk to each other across a package with deterministic latency and sufficient bandwidth. Without a common die-to-die interface, every chiplet integration is a custom engineering project. That does not scale.

graph TB

Die1[Compute Die] --> UCIe1[UCIe Interface]

Die2[Memory Die] --> UCIe2[UCIe Interface]

Die3[IO Die] --> UCIe3[UCIe Interface]

UCIe1 --> Substrate[Silicon Interposer / Substrate]

UCIe2 --> Substrate

UCIe3 --> Substrate

Substrate --> Package[Package / Board]

UCIe 1.0 defined a physical layer and a protocol layer for die-to-die communication. The physical layer specifies bump pitch, signaling rates, and channel reach for both standard and advanced packaging. The protocol layer supports CXL and PCIe semantics, which means chiplets can communicate using memory-semantic or IO-semantic protocols that the software ecosystem already understands. UCIe 2.0 pushed bandwidth higher and added features for multi-die topologies.

What actually matters here is mix-and-match. Today, if AMD builds a chiplet-based processor, every chiplet in that package is designed by AMD and fabbed at a process node AMD controls. UCIe's promise is a world where AMD could drop in a third-party AI accelerator chiplet, a memory chiplet from another vendor, and a networking chiplet from a third, all communicating over a standardized interface. The chiplet becomes a component you source, not a subsystem you design.

We are not there yet. The gap between specification and silicon is real. Testing and qualification for UCIe compliance is still maturing. The mechanical and thermal challenges of mixing chiplets from different sources in a single package are non-trivial. Yield, known-good-die testing, and supply chain logistics all need to catch up.

But the trajectory is clear. Intel, AMD, Arm, TSMC, Samsung, ASE, and dozens of others are on the UCIe consortium. The big players are aligning, which means the ecosystem will follow. IP vendors are building UCIe PHYs. EDA companies are adding UCIe-aware design flows.

The companies paying attention are the ones designing their chiplets with UCIe interfaces today, even before the ecosystem fully materializes. When the switch flips, they will be ready. Everyone else will be scrambling to redesign.

Get Chiplet Ecosystem in your inbox

New posts delivered directly. No spam.

No spam. Unsubscribe anytime.